Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

# Fast Simulation of SystemC Designs with Scoot

Nicolas Blanc, Daniel Kroening

www.cprover.org/scoot

Supported by Intel and SRC

Monday, 05 October 2009

### **Theme of the Presentation**

Utilization of the semantics of SystemC for Simulation speedup.

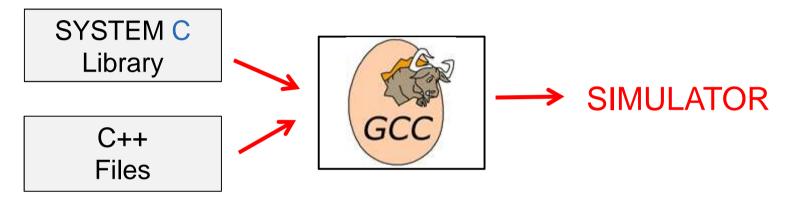

- System Description Language

- Based C++

- Compilation using g++

- IEEE Std.

SYSTEM C

- Compiler for SystemC

- www.cprover.org/scoot

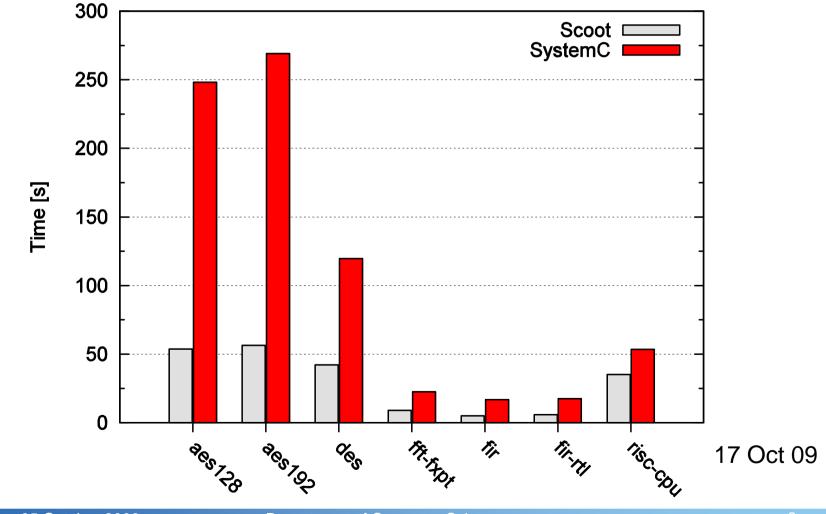

#### Execution Time (Oct 09, Linux 3Ghz, gcc 4.2.4, Linux)

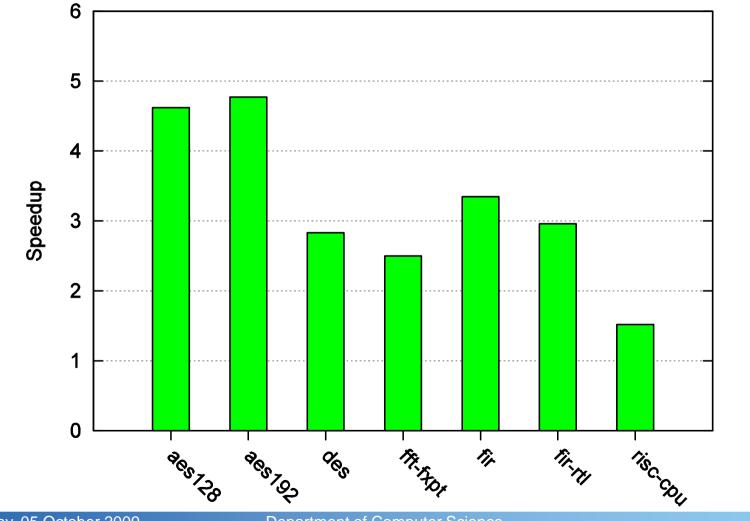

#### **Simulation Speedup**

### Outline

- Overview of SystemC

- Overview of Scoot

- Demo AES128

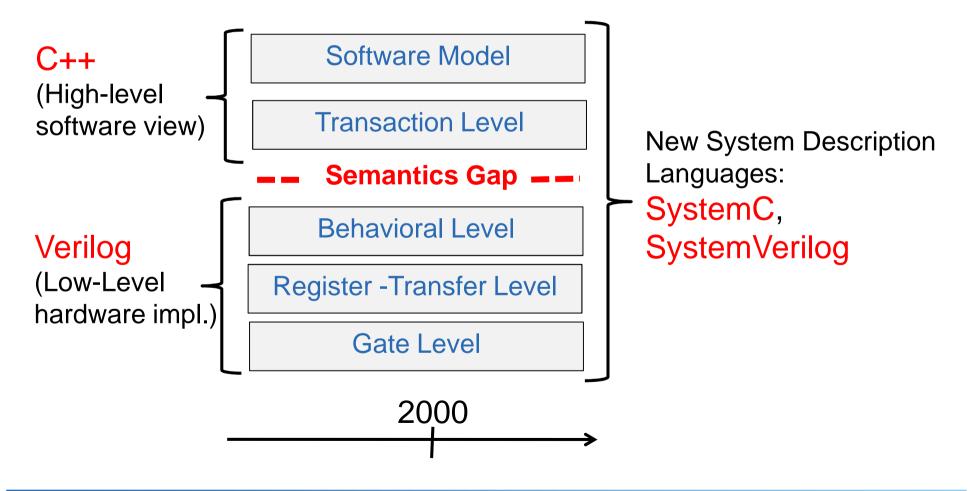

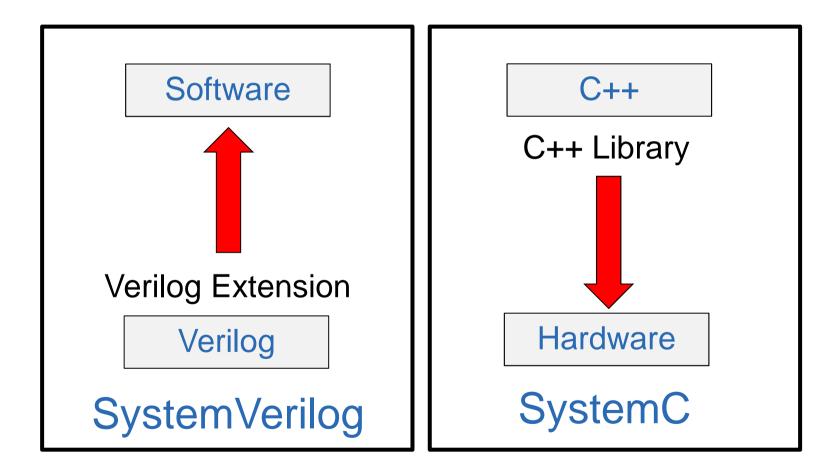

# **System Description Languages**

### SystemC versus SystemVerilog

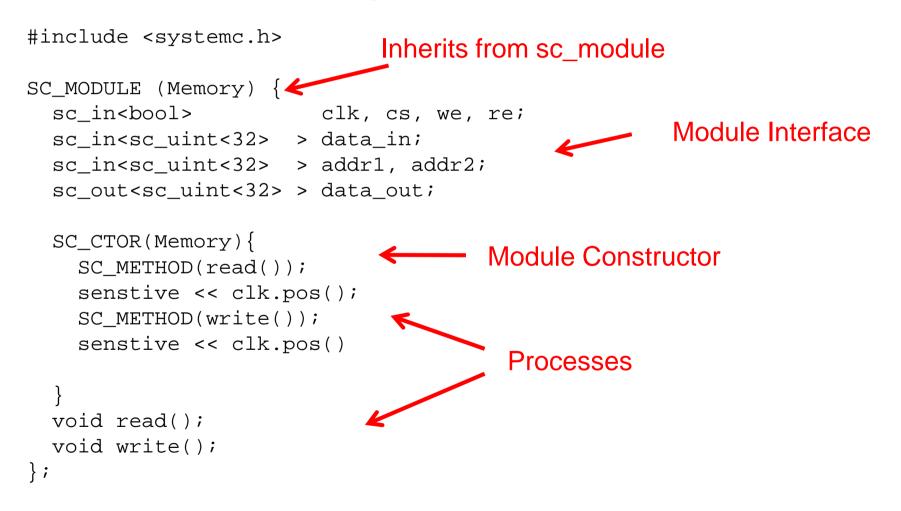

#### **Example: Memory Module**

```

int sc main(int argc, char* argv[])

{

Signals

sc clock clk;

sc_signal<bool> cs, re, we;

. . .

Modules

Memory mem(« MEMORY »);

Testbench tb(« TEST BENCH »);

mem.clk(clk);

Port Binding

mem.cs(cs); mem.re(re); mem.we(we);

. . .

sc start(10,SC US);

——— Start Simulation

return 0;

```

SystemC Simulation:

g++ main.cpp memory.cpp tb.cpp -lsystemc -o simulator

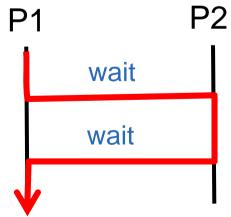

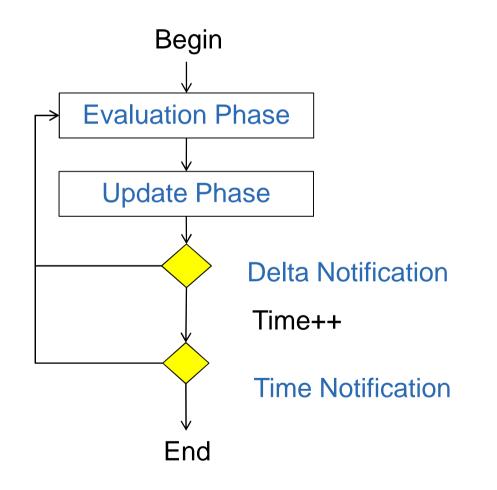

# **The Concurrency Model**

- Execution driven by events

- Cooperative Multitasking Model:

- Only one process running at a time

- No preemption!

### **The SystemC Scheduler**

#### **Observations**

- Elaboration of the Module Hierarchy at Runtime:

- Modules, processes, port binding,... The approach is flexible!

- C++ is fast: Fast execution of the processes!

- Yes ... but, GCC is not taking advantage of SystemC information!

- module hierachy, processes, and port binding.

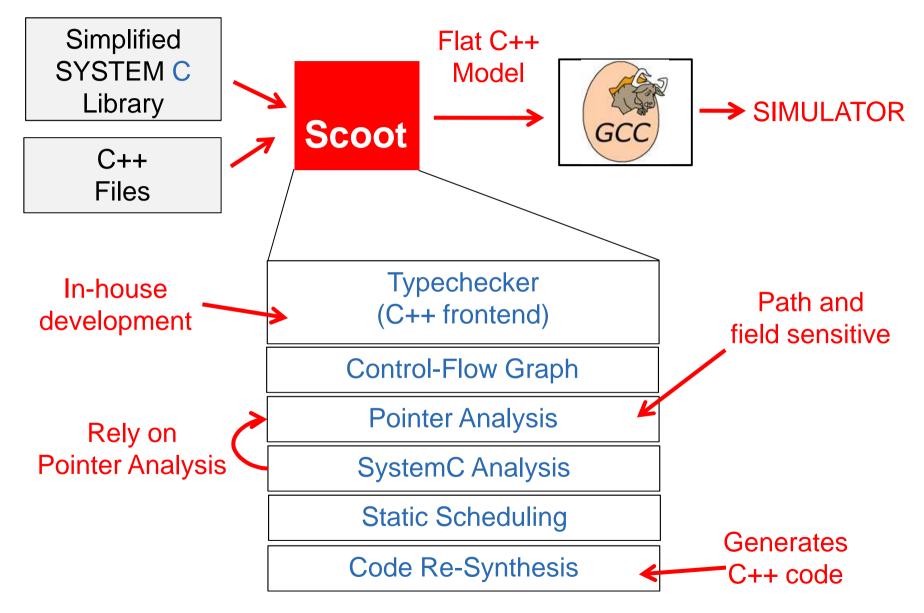

#### **Overview of Scoot**

- Scoot statically discovers:

- Module hierarchy, port binding, processes, and sensitivity lists.

- Simulation benefits from:

- Resolution of dynamic calls (static-scheduling)

- Suppression of dynamic data structures in the scheduler (lists, sets).

- Propagation of port binding information (pointers).

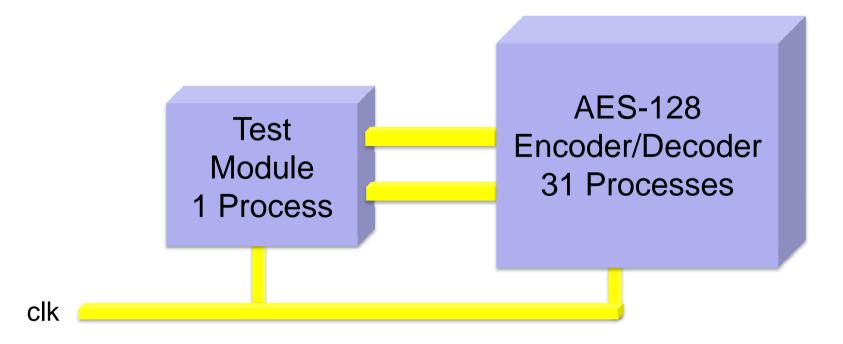

#### Demo

#### Benchmark: Encrypt, decrypt, and then display 128-bit vectors. Simulation Time: 800 Microseconds.

Scoot

## Conclusion

- Elaboration of the Module Hierarchy at Compile Time:

- We sacrifice some flexibility in exchange for

- significant simulation speedup, and

- we can now reason about SystemC models statically!

- Formal Verification, e.g., previous talk about static race analysis.

#### Thank You!

Scoot