Eidgenössische Technische Hochschule Zürich Swiss Federal Institute of Technology Zurich

## Race Analysis for SystemC using Model Checking

#### Nicolas Blanc, Daniel Kroening

www.cprover.org/scoot

Supported by Intel and SRC

© Department of Computer Science | ETH Zürich

Wednesday, 19 November 2008

Semiconductor

# **This Talk**

Formal race analysis for SystemC and its applications beyond verification.

- Race analysis: based on *Model Checking*

- Exhaustive Simulation: Partial-Order Reduction

#### Race

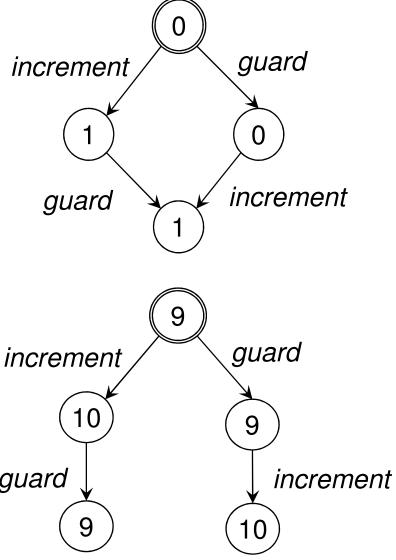

- Race in a concurrent system: the outcome of the computation depends on the scheduling

- Mechanism to model nondeterminism implicitly

- Design flaw: state corruption, deadlock,...

- Hard to verify: combinatorial explosion of schedules

- SystemC: language based on C++ for modeling concurrent systems

# **The SystemC Scheduler**

- Cooperative Multitasking Semantics:

- One process running at a time

- No preemption

- Execution driven by *events*

- Two kind of processes:

- *method process*: forbidden to suspend its execution

- *thread*: can wait for event notifications

## **Introductory Example**

```

SC_MODULE(Module){

sc_clock clk;

int pressure;

void guard(){

if(pressure == 10)

pressure = 9;

}

```

```

void increment() {

pressure++;

```

}

```

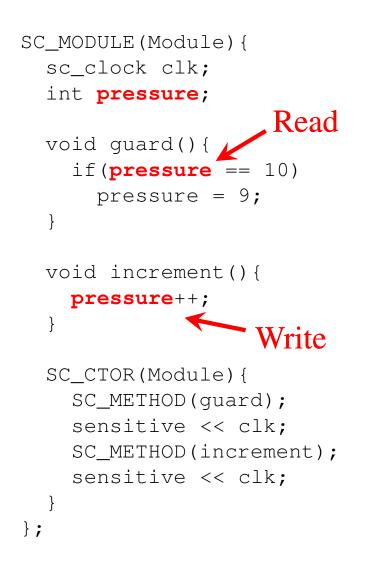

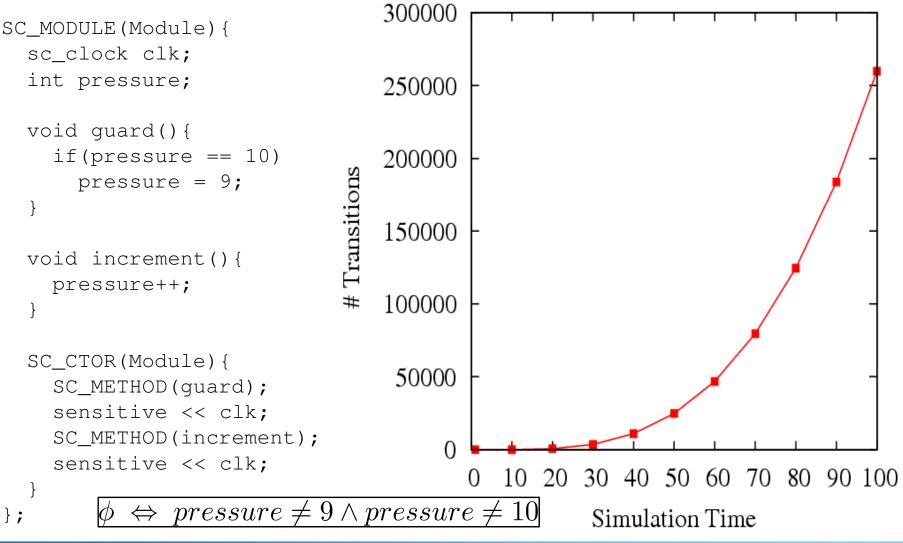

• Two processes: guard, increment

```

- Shared variable: pressure

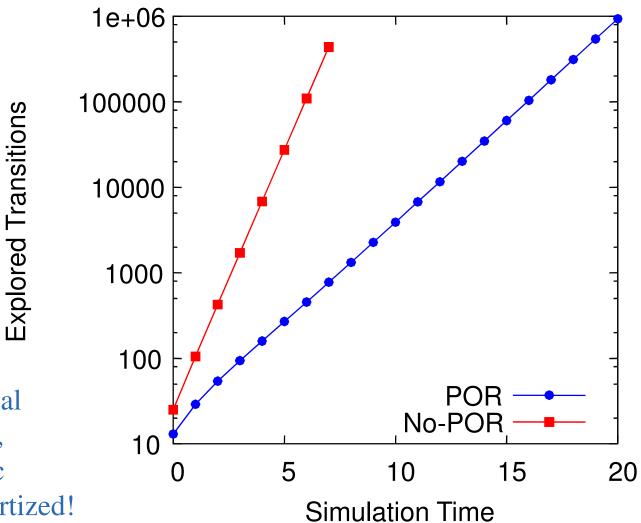

- Number of traces grows <u>exponentially</u> with the simulation time

- Pressure can exceed the limit.

```

SC_CTOR(Module){

SC_METHOD(guard);

sensitive << clk;

SC_METHOD(increment);

sensitive << clk;

}

};</pre>

```

```

SC_MODULE(Module) {

sc_clock clk;

int pressure;

void guard() {

if (pressure == 10)

pressure = 9;

}

void increment() {

pressure++;

}

SC_CTOR(Module) {

SC_METHOD(guard);

sensitive << clk;</pre>

SC_METHOD(increment);

guard

sensitive << clk;</pre>

}

};

```

Classic static analysis achieves no reduction!

```

SC_MODULE(Module) {

sc_clock clk;

int pressure;

void guard() {

if (pressure == 10)

pressure = 9;

void increment() {

pressure++;

}

SC CTOR(Module) {

SC_METHOD(quard);

sensitive << clk;</pre>

SC_METHOD(increment);

sensitive << clk;</pre>

};

```

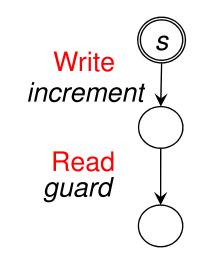

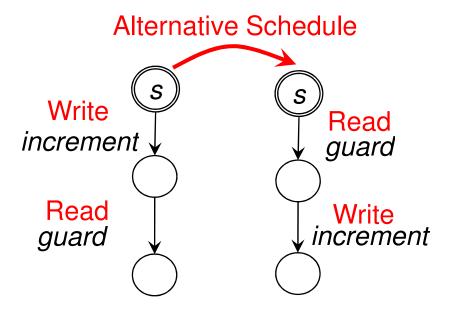

#### **Dynamic Partial-Order Reduction:**

```

SC_MODULE(Module) {

sc_clock clk;

int pressure;

void guard() {

if (pressure == 10)

pressure = 9;

void increment() {

pressure++;

}

SC CTOR(Module) {

SC_METHOD(quard);

sensitive << clk;</pre>

SC METHOD (increment);

sensitive << clk;</pre>

};

```

#### **Dynamic Partial-Order Reduction:**

# Runtime analysis achieves no reduction!

#### When are the processes independent?

```

SC MODULE(Module) {

sc_clock clk;

int pressure;

void guard() {

if(pressure == 10)

pressure = 9;

void increment() {

pressure++;

}

SC CTOR(Module) {

SC_METHOD(quard);

sensitive << clk;</pre>

SC_METHOD(increment);

sensitive << clk;</pre>

};

```

**Department of Computer Science**

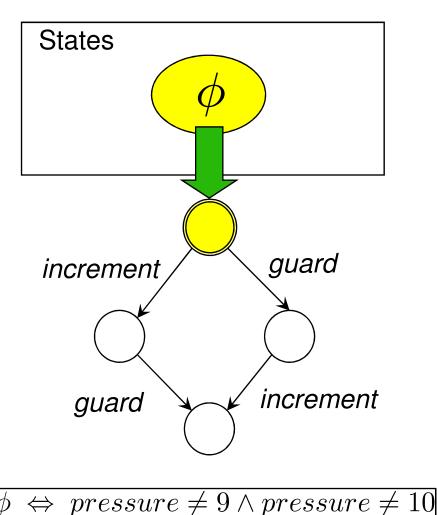

## Guarded Independence [C. Wang et al., TACAS 2008]

Derives directly from P. Godefroid's notion of conditional independence.

**Definitition**. Two transitions  $\alpha$  and  $\beta$  are guarded independent with respect to a guard  $\phi \subseteq S$  if and only if for all  $s \in \phi$  the following hold:

- 1.  $\alpha \in Enabled(s) \Rightarrow$   $\beta \in Enabled(s) \Leftrightarrow \beta \in Enabled(\alpha(s))$ 2.  $\beta \in Enabled(s) \Rightarrow$   $\alpha \in Enabled(s) \Leftrightarrow \alpha \in Enabled(\beta(s))$ 3.  $\alpha, \beta \in Enabled(s) \Rightarrow \alpha(\beta(s)) = \beta(\alpha(s))$

- Contribution:

- Formal technique to compute  $\phi$  for SystemC

- Applications: formal verification, simulation, and testing

#### **Exploration with Partial-Order Reduction**

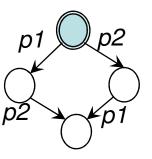

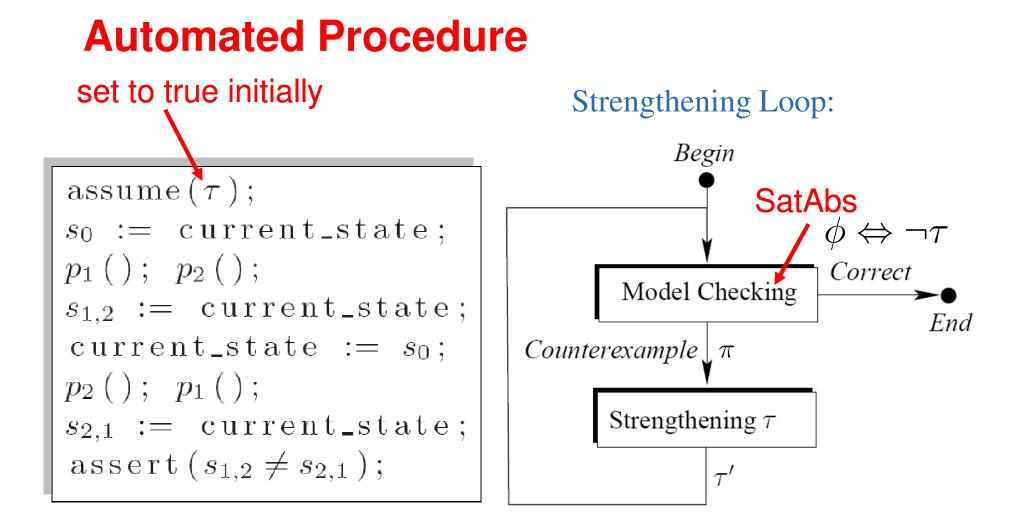

# **Computation of Guarded Independence**

<u>IDEA</u>: exploit the cooperative execution model of SystemC to compute  $\phi$  iteratively using a harness.

$$s_0 := current\_state;$$

$p_1(); p_2();$

$s_{1,2} := current\_state;$

$current\_state := s_0;$

$p_2(); p_1();$

$s_{2,1} := current\_state;$

$assert(s_{1,2} \neq s_{2,1});$

We have found a trace such that:

- 1. the execution of *p1*, *p2* terminates, and

- 2. the order of execution is irrelevant.

Counterexample

$\pi$

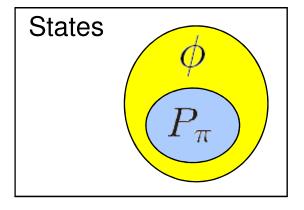

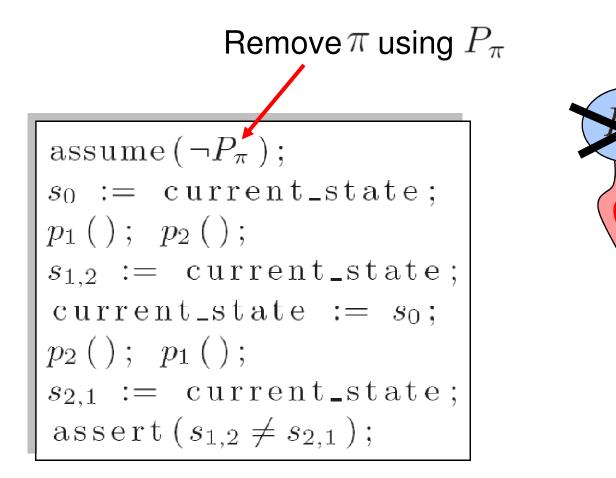

# **Using the Counterexample**

$P_{\pi}$  is an under-approximation of  $\,\phi$  :

Weakest precondition:

$$P_{\pi} = wp(\pi, s_{1,2} = s_{2,1})$$

If  $P_{\pi}$  holds in the pre-state, then:

- 1. the execution terminates, and

- 2. the execution order is irrelevant.

$\Gamma_{\pi}$

$\pi$

# **Computing Preconditions**

Hoare's rule for assignments:  $\{P[v/E]\}\ v := E;\ \{P\}$ Postcondition Precondition Command  $\{y < x\}$ tmp := x; $\{y < tmp\}$ x := y;  $\{x < tmp\}$ y := tmp; $\{x < y\}$

Wednesday, 19 November 2008

**Department of Computer Science**

#### Strengthening the set of initial states

$\pi$

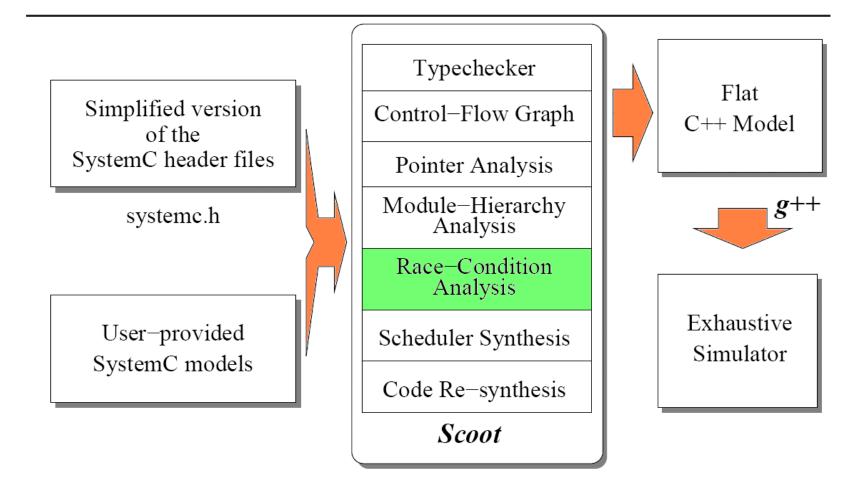

#### **Scoot: Research Compiler for** *SystemC*

# **Benchmark: Memory Components**

- Often subject to race phenomenon

- Present in most electronics designs:

- FIFOs, bridges, processors

## **Asynchronous Dual Port RAM**

```

SC_MODULE (ram_dp_ar_aw) {

. . .

void READ 0 ();

void WRITE_0 ();

void READ 1 ();

2x2 processes

void WRITE_1 ();

};

void READ_0 () {

if (cs 0.read() && oe 0.read() && !we 0.read())

data_0 = mem[address_0.read()];

}

exclusive RD/WR

void WRITE 0 () {

if (cs 0.read() && we 0.read())

mem[address 0.read()] = data 0.read();

```

#### **Benchmark Results**

| Processes                                | Indep? | # Stren. | Predicates | $\operatorname{SMV}$        | Total Time                   |

|------------------------------------------|--------|----------|------------|-----------------------------|------------------------------|

| Rd1, Rd0                                 | yes    | 16       | 23         | 13s                         | $40\mathrm{s}$               |

| Wr0, $Rd0$                               | yes    | 5        | 38         | 12s                         | $50\mathrm{s}$               |

| Wr0, $Rd1$                               | no     | 12       | 169        | 17m~6s                      | $28\mathrm{m}$               |

| Wr1, Rd0                                 | no     | 12       | 169        | $28\mathrm{m}~38\mathrm{s}$ | $39\mathrm{m}\ 18\mathrm{s}$ |

| Wr1, Rd1                                 | yes    | 5        | 38         | 12s                         | 53s                          |

| Wr1, Wr0                                 | no     | 9        | 104        | $38\mathrm{s}$              | 5m~24s                       |

| $\operatorname{run}, \operatorname{Rd0}$ | yes    | 12       | 69         | $3\mathrm{m}$               | 3m $47s$                     |

| run, Rd1                                 | yes    | 12       | 69         | 2m $47s$                    | 3m $35s$                     |

| run, Wr0                                 | yes    | 9        | 75         | 2m $17s$                    | 3m $35s$                     |

| run, Wr1                                 | yes    | 9        | 75         | 2m $17s$                    | 3m $35s$                     |

$\phi \Leftrightarrow true \int$

#### Linux, Intel Xeon 3GHz.

# **Trading Precision for Time**

| Processes                   | Indep?   | # Stren. | Predicates                               | SMV               | Total Time                                                                |

|-----------------------------|----------|----------|------------------------------------------|-------------------|---------------------------------------------------------------------------|

| Wr0, Rd1           Wr0, Rd1 | no<br>no | 12<br>11 | $\begin{array}{c} 169 \\ 42 \end{array}$ | $\frac{17m}{27s}$ | $\begin{array}{c} 28\mathrm{m} \\ 1\mathrm{m} \ 30\mathrm{s} \end{array}$ |

|                             | no<br>no | 12<br>11 | $\begin{array}{c} 169 \\ 42 \end{array}$ | 28m $3827s$       | $39m\ 18s$ $1m\ 30s$                                                      |

#### **Exhaustive Simulation**

Due to the combinatorial explosion of schedules, the time spent for static analysis is rapidly amortized!

## Conclusion

- "Formal" has applications beyond property checking: optimization, simulation, testing

- Partition the system into "small" verification tasks

- Distribute those tasks among many cores

- Trade precision for time

- Pragmatic approach to successful application of formal engines at high abstraction levels

## **Related Work**

"Partial order reduction for scalable testing of SystemC TLM designs",

Sudipta Kundu et al., DAC 2008

- "Automatic generation of schedulings for improving the test coverage of systems-on-a-chip", Claude Helmstetter et al., FMCAD 2006

- "Dynamic partial-order reduction for model checking software", Cormac Flanagan et al., SIGPLAN, 2005

- *Patrice Godefroid's PhD thesis, 1994*